# **Exogenous Coordination of Concurrent Software Components** with JavaBIP

Simon Bliudze<sup>1\*</sup>, Anastasia Mavridou<sup>2</sup>, Radoslaw Szymanek<sup>3</sup> and Alina Zolotukhina<sup>1</sup>

<sup>1</sup>Ecole polytechnique fédérale de Lausanne 1015, Lausanne, Switzerland <sup>2</sup>Institute for Software Integrated Systems, Vanderbilt University, Nashville, TN 37235, USA Crossing-Tech S.A., EPFL Innovation Park, 1015, Lausanne, Switzerland

#### **SUMMARY**

A strong separation of concerns is necessary in order to make the design of domain-specific functional components independent from cross-cutting concerns, such as concurrent access to the shared resources of the execution platform. Native coordination mechanisms, such as locks and monitors, allow developers to address these issues. However, such solutions are not modular, they are complex to design, debug and maintain. We present the JavaBIP framework that allows developers to think on a higher level of abstraction and clearly separate the functional and coordination aspects of the system behavior. It implements the principles of the BIP component framework rooted in rigorous operational semantics. It allows the coordination of existing concurrent software components in an exogenous manner, relying exclusively on annotations, component APIs and external specification files. We introduce the annotation and specification syntax of JavaBIP and illustrate its use on realistic examples; present the architecture of our implementation, which is modular and easily extensible; provide and discuss performance evaluation results. Copyright © 2016 John Wiley & Sons, Ltd.

Received ...

KEY WORDS: BIP; JavaBIP; Component coordination; Concurrency; Modularity

Prepared using speauth.cls [Version: 2010/05/13 v3.00]

<sup>\*</sup>Correspondence to: EPFL IC IINFCOM LCA2, Station 14, 1015 Lausanne, Switzerland. E-mail: Simon.Bliudze@epfl.ch

# CONTENTS

| 1 |      | oduction                                                    | 3  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | The BIP Component Framework                                 | 4  |

|   | 1.2  | Paper Contribution and Structure                            | 4  |

| 2 | Java | aBIP Design Workflow                                        | 5  |

| 3 | Java | aBIP by examples                                            | 6  |

|   | 3.1  | Camel routes                                                | 7  |

|   | 3.2  | Publish-Subscribe server                                    | 10 |

|   | 3.3  | Trackers and Peers example                                  | 12 |

| 4 | The  | oretical foundations                                        | 13 |

|   | 4.1  | Component model without data                                | 13 |

|   |      | 4.1.1 Components and glue                                   | 13 |

|   |      | 4.1.2 Connectors                                            | 14 |

|   |      | 4.1.3 Boolean encoding of the connectors and macro notation | 15 |

|   |      | 4.1.4 Macro notation based on component types               | 17 |

|   | 4.2  | Extension of the model with data                            | 19 |

|   |      | 4.2.1 Components with data                                  | 19 |

|   |      | 4.2.2 Composition                                           | 21 |

| 5 | Syst | em specification                                            | 22 |

|   | 5.1  | Behavior specification                                      | 22 |

|   | 5.2  | Glue specification                                          | 23 |

|   | 5.3  | Data-wire specification                                     | 26 |

| 6 | Imp  | lementation                                                 | 26 |

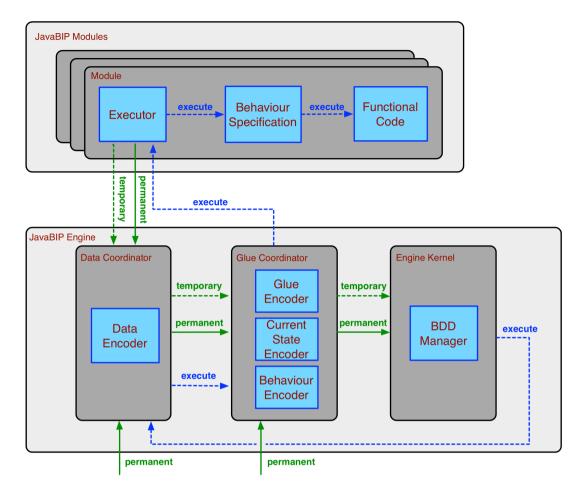

|   | 6.1  | JavaBIP module                                              | 27 |

|   | 6.2  | JavaBIP engine                                              | 28 |

|   |      | 6.2.1 Engine kernel                                         | 28 |

|   |      | 6.2.2 Glue coordinator                                      | 29 |

|   |      | 6.2.3 Data coordinator                                      | 30 |

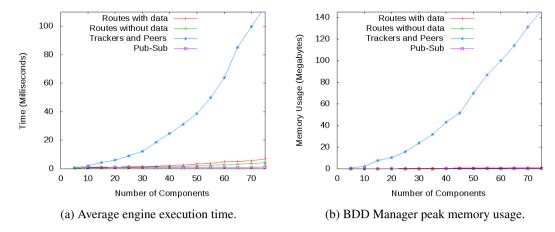

|   | 6.3  | Experimental evaluation                                     | 30 |

| 7 | Rela | ated work                                                   | 31 |

| 8 | Con  | clusion and Future Work                                     | 35 |

Softw. Pract. Exper. (2016) DOI: 10.1002/spe

## 1. INTRODUCTION

When building large concurrent systems, one of the key difficulties lies in coordinating component behavior and, in particular, management of the access to shared resources of the execution platform. This is well illustrated by our motivating use-case, which consists in managing the memory usage by a set of Camel routes [1]. Camel routes are extensively utilized in Connectivity Factory<sup>TM</sup>—the flagship product of Crossing-Tech S.A. A Camel route connects a number of data sources to transfer data among them. The data can be fairly large and may require additional processing. Hence, Camel routes share and compete for memory. Without additional coordination, simultaneous execution of several Camel routes can lead to OutOfMemory exceptions, even when each route has been tested and sized appropriately on its own.

In all mainstream programming languages, including Java and C++, basic coordination primitives are implemented as built-in features of the language [2, 3]. Different variations of locks, semaphores and monitors are used to express coordination constraints. However, these low-level primitives are mixed up with the functional code, forcing developers to keep both aspects simultaneously in mind—not only at design time, but also during debugging and maintenance. Since in concurrent environments it is practically infeasible to envision all possible execution scenarios, synchronization errors can result in race conditions and deadlocks.

Furthermore, an observable trend in software engineering is the increasing utilization of the declarative design techniques. Developers provide specifications of *what* must be achieved, rather than *how* this must be achieved. These specifications are then interpreted by the corresponding engines, which generate—often on the fly—the corresponding software entities. It is not always possible to instrument or even access the actual source code. Even if the code is generated explicitly, it is usually not desirable to modify it, since this can lead to a considerable increase of maintenance costs. This precludes the use of low-level primitives for the coordination of concurrent components that have to be reusable in different configurations and assemblies. Therefore, the problem of coordinating concurrent components calls for an exogenous solution that would allow developers to think on a higher level of abstraction, separating functional and coordination aspects of the system behavior.

To address this concurrency challenge, we have developed JavaBIP—a Java adaptation of the BIP (Behavior, Interaction, Priority) framework [4]—relying on the following observations. Domain specific components, such as Camel routes, have states (e.g., idle, working, suspended) that are known to component users with domain expertise. Furthermore, components always provide APIs that allow programs to invoke operations (e.g., suspend or resume) in order to change their state, or to be notified when the component changes the state spontaneously. Thus, component behavior can be represented by Finite State Machines (FSM). An FSM has a finite set of states and a finite set of transitions between these states. Transitions are associated with calls to API functions, which force a component to take an action, or with event notifications that allow reacting to external events coming from the environment. Since such states and transitions have intuitive meaning for developers, representing components as FSMs is an adequate level of abstraction for reasoning about their behavior.

To use JavaBIP, developers must provide—for the relevant components—the corresponding FSMs in the form of annotated Java classes. These classes are used to drive the interaction with the corresponding components through their provided APIs. The FSMs describe the protocol that must be respected to access a shared resource or use a service provided by a component, ensuring correct utilization of component interfaces.

For component coordination, JavaBIP provides two primitive mechanisms: 1) multi-party synchronization of component transitions and 2) asynchronous event notifications. The latter embodies the reactive programming paradigm. In particular, JavaBIP extends the Actor model [5], since event notifications can be used to emulate asynchronous messages. Providing the synchronization of component transitions as a primitive mechanism gives the developers a powerful and flexible tool to manage coordination.

Softw. Pract. Exper. (2016)

JavaBIP clearly separates system-wide coordination policies from the component behavior. Interaction constraints, defining the possible synchronizations among transitions of different components, are specified in XML configuration files independently from the design of individual components. For coordination scenarios that require global state information, dedicated *monitor* components can be added. This allows one to centralize all the information related to coordination in one single location, instead of distributing it across the components. Coordination is applied in an exogenous manner, relying totally on component APIs. Furthermore, JavaBIP components do not carry coordination logic that relies on the characteristics of any specific execution environment.

Thus, JavaBIP addresses the major coordination issues by providing strong modularity, which, in its turn, enables maximal reusability of components and facilitates the management of product variants. The separation of functional and coordination aspects greatly reduces the burden of system complexity. Finally, integration with the BIP framework (cf. Section 2), allows the use of existing tools [6, 7] for deadlock-detection and model checking, ensuring the correctness of generated systems.

# 1.1. The BIP Component Framework

JavaBIP implements the BIP coordination mechanism [4]. BIP is a framework for component-based design of correct-by-construction applications. It provides a simple, but powerful mechanism for coordination of concurrent components by superposing three layers: Behavior, Interaction, and Priority. The first layer describes the behavior of components as FSMs having transitions labeled with *ports* and extended with data stored in local variables. Ports form the interface of a component and are used to define its interactions with other components. They can also export part of the local variables, allowing access to the component's data. The second layer defines component coordination by means of *interaction models*, i.e., sets of interactions. Interactions are sets of ports that define allowed synchronizations between components. An interaction model is defined in a structured manner by using connectors [8]. For each interaction, a connector also specifies how the data is retrieved, filtered and updated in each of the participating components. In particular, a Boolean guard can be associated to an interaction. The interaction is only enabled if the data provided by the components satisfies the guard [9]. In the third layer, priorities are used to impose scheduling constraints and to resolve conflicts when multiple interactions are enabled simultaneously. Interaction and Priority layers are collectively called *Glue*.

The execution of a BIP system is driven by the BIP engine applying the following protocol in a cyclic manner:

- 1. Upon reaching a state, each component notifies the BIP engine about the possible outgoing transitions:

- 2. The BIP engine picks an interaction satisfying the glue specification, performs the data transfer and notifies all the involved components;

- 3. The notified components execute the functions associated with the corresponding transitions.

## 1.2. Paper Contribution and Structure

In [10], we have published a preliminary, proof-of-concept implementation of our approach focusing on the adaptation of the BIP coordination primitives in the Java software-engineering context. The main difference of that implementation from the classical BIP was the addition of spontaneous transitions, which allow components to update their state based on the events occurring in their environment (cf. Section 3).

This paper presents a new implementation, which has been almost completely redesigned and extended as follows. First of all, in order to make JavaBIP applicable to practical systems, we have extended the behavior specification and the coordination mechanisms to explicitly handle data and data transfer between components. In order to give developers full control of data exposure and use within the interactions among components, we have implemented a simplified form of data transfer, which, however, has the same expressive power as in the classical BIP.

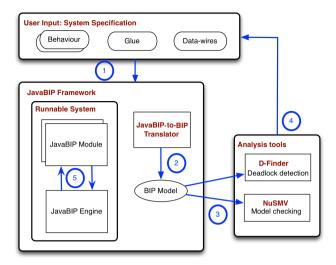

Figure 1. JavaBIP design workflow.

In order to implement the data transfer and facilitate future extensions of the JavaBIP framework, we have developed a new modular and extensible engine, consisting of a symbolic kernel and a *coordinator stack*. At each execution cycle, the kernel determines the next interaction by solving the combined system constraints. Each coordinator is responsible for 1) encoding a particular type of constraints into a form that the kernel can process and 2) interpreting the relevant part of the solution provided by the kernel to drive the component execution. We implemented two coordinators: the Glue Coordinator, implementing the BIP coordination mechanism, and the Data Coordinator, controlling data transfer among components.

We provide a formalization of the semantic model underlying the JavaBIP implementation. Although this formalization is based on the previous work on BIP [4, 8, 11], it is adapted and extended to reflect the specificities of JavaBIP. Finally, we have designed new examples that we use to illustrate the JavaBIP modelling concepts and evaluate the overhead induced by the engine.

The rest of the paper is structured as follows. Section 2 presents the JavaBIP design workflow. Section 3 provides examples of JavaBIP models, explaining how the proposed design methodology can be applied in practice. Section 4 defines the formal semantic model underlying the JavaBIP design.† Section 5 presents the annotations and XML constructs used to design JavaBIP specifications. Section 6 describes the implemented software architecture and presents performance results. Section 7 presents the related work. Section 8 summarizes the results and future work directions.

# 2. JAVABIP DESIGN WORKFLOW

Figure 1 shows the steps of the JavaBIP design flow. In the step ①, the *system specification* is designed, consisting of the following annotated Java classes and XML configuration files:

A behavior specification for each component, given by an FSM extended with ports and data.

This is provided as an annotated Java class, whereof the methods can call APIs provided by the coordinated components.

Softw. Pract. Exper. (2016)

<sup>&</sup>lt;sup>†</sup>The formal material in Section 4 can be omitted by readers interested only in understanding how to use the JavaBIP framework.

- The *glue specification*, which is the interaction model of the system that specifies how the transitions of different components must be synchronized. This is provided as an XML configuration file.

- Optionally, data transfer can be defined, by providing the *data-wire specification* for each data variable of every component, that specifies which data are exchanged between components. This is provided as an XML configuration file.

The optional analysis loop starts in step ②, where the system specification is automatically translated into an equivalent model of the system expressed in the BIP language.<sup>‡</sup> This model can then be verified for deadlock freedom or other safety properties (we provide examples in Section 3.1 and Section 3.2), using DFinder [6], ESST or nuXmv [7] (step ③). Other analyses can be performed using any tool for which a model transformation from BIP is available. If the required safety properties are not satisfied by the model, the specification can be refined by the developers (step ④) and analyzed anew. Finally, when developers are satisfied with the design, the refined specification can be executed (step ⑤). Steps ②, ③, and ④ are optional and can be repeated several times.

As shown in Figure 1, the *runnable system* consists of two major parts: the *engine* and several *modules*, one for each component to be coordinated. Each module is composed of a dedicated executor, a behavior specification and the corresponding functional code of the component (cf. Figure 15). The executor has access to the behavior specification of the component and uses it to drive the module execution. The behavior specification of each component along with the glue and data-wire specifications are provided to the engine. The engine orchestrates the overall execution of the system by deciding which component transitions must be executed at each cycle. It then notifies the executors of the selected transitions and they make the corresponding calls to the functional code.

## 3. JAVABIP BY EXAMPLES

In this section, we provide three examples illustrating the modeling concepts of JavaBIP. The Camel routes example (Section 3.1) illustrates the basic notions, i.e. the FSMs, the three kinds of transitions and simple connectors. The Publish-Subscribe server example (Section 3.2) illustrates use of notifications to encode Actor-like asynchronous communication. Finally, Trackers and Peers (Section 3.3) is a toy example intentionally designed with a complex coordination pattern involving multiparty interaction. These examples are also used in the rest of the paper to illustrate the proposed annotation language and, in Section 6.3, to evaluate the overhead incurred by using the JavaBIP framework. In particular, the complexity of the coordination pattern of the Trackers and Peers example will allow us to subject the JavaBIP engine to a stress test under high coordination load and evaluate the practical limitations of the current implementation.

FSM transitions can be of three types: *enforceable, spontaneous* and *internal*. Enforceable transitions are controlled by the engine. At each execution cycle, executors inform the engine about enforceable transitions offered by the components in their current state. The engine decides which of these should be executed and notifies the executors of its decision. Spontaneous transitions are used to take into account changes in the environment and, therefore, they are not announced to the engine but rather executed after detection of events in the environment of the component. Finally, internal transitions allow behavior specifications to update its state based on internal information—when enabled, they are executed immediately. Spontaneous and internal transitions cannot be used for synchronization with other components.

Interaction models can be represented in many equivalent ways. Among these are connectors [8] and Boolean formulas on variables representing port participation in interactions [12]. Connectors are most appropriate for graphical design and interaction representation, whereas Boolean formulas

Softw. Pract. Exper. (2016)

<sup>&</sup>lt;sup>‡</sup>We have developed a prototype of the JavaBIP-to-BIP transformation tool. However, its presentation is not in the scope of this paper.

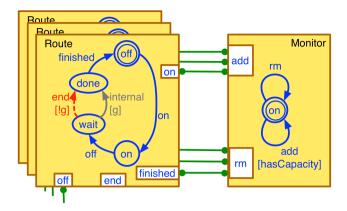

Figure 2. JavaBIP models of three routes and a monitor.

are most appropriate for manipulation and efficient encoding. In this paper, we use the graphical notation in the figures illustrating the examples. Equivalent notation based on Boolean macros (cf. Section 5) is used to define the allowed synchronizations in the glue specification.

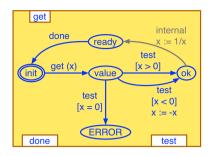

In Figures 2, 5 and 8, the initial states of all FSMs are denoted by a double circle; Boolean guards on transitions are shown in square brackets; enforceable transitions are shown with solid blue arrows, spontaneous transitions with dashed red arrows and internal transitions with solid grey arrows.

## 3.1. Camel routes

A Camel route [1] transfers data among a number of data sources. The data can be fairly large and may require additional processing. Hence, Camel routes share and compete for memory. Without additional coordination, simultaneous execution of several Camel routes can lead to OutOfMemory exceptions, even when each route has been tested and sized appropriately on its own. The Camel API provides the methods resumeRoute and suspendRoute to control the activation of a route. For simplicity, we assume here that the memory used by an active route is known, whereas the memory used by a suspended route is negligible.

Consider the Route and Monitor models, shown in Figure 2. Our goal is to limit the number of routes running simultaneously to ensure that the available memory is sufficient for the safe functioning of the system. To achieve this, we introduce an additional monitor component. The behavior specifications of the Route and Monitor component types are shown in Figures 3 and 4 respectively. The precise syntax is explained in Section 5.1.

The Route model, shown in the left-hand side of Figure 2, has four states: off, on, wait and done. Its initial state is off. When the route is at state off, it can start working by executing the on transition. Respectively, when the route is at state on, it can suspend its work by executing the off transition. The on and off transitions are both enforceable (Figure 3: lines 3–4) and are associated with the resumeRoute and suspendRoute methods of the Camel API (Figure 3: lines 19–27).

Following the call to suspendRoute associated with the transition off, the route moves to the state wait. At this point, if the route has finished processing the previous data batch, it can be suspended immediately—represented by the internal transition to the done state (Figure 3: lines 32–33). Otherwise, the internal transition is disabled. Instead, to move to state done, the route has to wait for the processing termination event, associated with the spontaneous transition end (Figure 3: lines 29–30). The guard g (Figure 3: lines 38–42) is used to check whether the route has finished processing.

The Monitor model, shown in the right-hand side of Figure 2, has only one state and two enforceable transitions: add (Figure 4: lines 16-20) for adding running routes and rm (Figure 4: lines 22-25) for removing them. The add transition has the guard hasCapacity (Figure 4:

```

1 @Ports({

@Port(name = "end", type = PortType.spontaneous),

@Port(name = "on", type = PortType.enforceable),

@Port(name = "off", type = PortType.enforceable),

3

@Port(name = "finished", type = PortType.enforceable)

5

6 })

7 @ComponentType(initial = "off", name = "Route")

8 public class Route implements CamelContextAware {

10

private CamelContext camelContext;

11

private String routeId;

12

private int deltaMemory = 100; // Dummy value, for the sake of simplicity

13

14

public Route(String routeId, CamelContext camelContext) {

15

this.routeId = routeId;

16

this.camelContext = camelContext;

17

18

19

@Transition(name = "on", source = "off", target = "on")

2.0

public void startRoute() throws Exception {

21

camelContext.resumeRoute(routeId);

22

23

2.4

@Transition(name = "off", source = "on", target = "wait")

25

public void stopRoute() throws Exception {

26

camelContext.suspendRoute(routeId);

27

28

29

@Transition(name = "end", source = "wait", target = "done", guard = "!g")

30

public void spontaneousEnd() {} // "!q" in the guard above means "not q"

31

32

@Transition(name = "", source = "wait", target = "done", guard = "g")

33

public void internalEnd() {}

34

35

@Transition(name = "finished", source = "done", target = "off")

36

public void finishedTransition() {}

37

38

@Guard(name = "q")

39

public boolean isFinished() {

40

return camelContext.getInflightRepository().

size(camelContext.getRoute(routeId).getEndpoint()) == 0;

41

42

43

44

@Data(name = "deltaMemoryOnTransition",

45

accessTypePort = AccessType.allowed, ports = { "on", "finished" })

46

public int deltaMemoryOnTransition() {

47

return deltaMemory;

48

49 }

```

Figure 3. Annotations for the Route component type.

lines 27–30) that checks whether the available memory limit of the system, defined through the constructor of the MemoryMonitor class (Figure 4: lines 12–14), is sufficient for adding more running routes.

The complete system consists of several routes and one monitor. The Route model is the same for all routes and the monitor is connected to all of them in the same manner. The port on of each route component must synchronize with the port add of the monitor. This means that when a route component is executing the on transition, the monitor component must execute the add transition simultaneously. Thus, if the available memory capacity is not sufficient, the on transition is blocked. Since the add port of the monitor is connected to the on ports of several different routes by binary connectors, it must only synchronize with one of them at a time. Similarly, transition finished of

```

1 @Ports({

@Port(name = "add", type = PortType.enforceable),

3

@Port(name = "rm", type = PortType.enforceable)

4 })

6 @ComponentType(initial = "on", name = "MemoryMonitor")

public class MemoryMonitor {

8

final private int memoryLimit;

9

10

private int currentCapacity = 0;

11

12

public MemoryMonitor(int memoryLimit) {

13

this.memoryLimit = memoryLimit;

14

15

@Transition(name = "add", source = "on", target = "on",

16

quard = "hasCapacity")

17

18

public void addRoute(@Data("memoryUsage") Integer deltaMemory) {

19

currentCapacity += deltaMemory;

20

21

22

@Transition(name = "rm", source = "on", target = "on")

public void removeRoute(@Data(name="memoryUsage") Integer deltaMemory) {

23

2.4

currentCapacity -= deltaMemory;

2.5

26

@Guard(name = "hasCapacity")

27

28

public boolean hasCapacity(@Data("memoryUsage") Integer memoryUsage) {

29

return currentCapacity + memoryUsage < memoryLimit;</pre>

30

31 }

```

Figure 4. Annotations for the Monitor component type.

each route must be synchronized with the transition rm of the monitor. Notice that the specification of synchronizations between the on-add transitions and rm-finished transitions is not part of the behavior specification presented in Figures 2 and 4. These synchronizations are included in the glue specification presented in Figure 13.

At each execution cycle, the monitor decides whether there is sufficient amount of memory in the system to add another route. To do that, data are being exchanged between the non-running routes and the monitor. Every route has a value of how much memory it consumes if it resumes working (Figure 3: lines 44–48) and sends this to the monitor. The monitor then decides by computing the hasCapacity guard value and informs the JavaBIP engine of its decision. Data exchange between the routes and the monitor happens if the on-add synchronization can be executed, i.e., some of the routes are at state off. Additionally, data exchange occurs before the finished-rm synchronization is executed: the corresponding route tells the monitor how much memory it will release upon suspending its execution.

Notice that the access control functionality implemented in this example, can also be implemented in an actor-based framework, through a synchronization on a future. Indeed, by implementing the monitor as an actor capable of serving the request hasCapacity, it is sufficient to send such a request before resuming a route and store the returned Boolean yes-or-no value in a future, then immediately consulting this future as part of a branching condition. This would block the route activation until the reply from the monitor is available, effectively achieving a synchronization between the route and the monitor. The advantage of the JavaBIP approach is that—contrary to the solution using a Boolean future—it does not require the synchronization to be hardcoded in the route specification: in the ideal situation, where infinite memory is available, exactly the same BIP specification of the routes can be used without the monitor and the corresponding glue. Similarly, if, at a later stage in the project or for the purpose of debugging, the developer needed to introduce a logger component to keep track of route management operations, this could be achieved simply

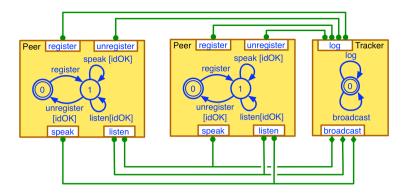

Figure 5. JavaBIP models of a publish-subscribe server.

by defining the corresponding BIP specification and replacing binary synchronizations (Figure 2) by ternary ones. As will be explained in Section 5.2, this latter operation only involves editing an XML configuration file, which can even be performed by a system administrator, without requiring an intervention by a developer.

The complete model of this example is deadlock free and satisfies the following safety property: 'A route cannot be added unless sufficient memory capacity is available'. Notice that this property is enforced on an arbitrary number of routes by synchronizing them in the predefined manner with an additional Monitor component. The Monitor component together with the associated connectors (Figure 2) forms a pattern, called an architecture. In [13, 14], the authors have developed a compositional theory of architectures—illustrated by a large case study in [15]—that allows the definition and composition of such patterns to enforce arbitrary combinations of safety properties.

## 3.2. Publish-Subscribe server

In this section, we present a JavaBIP implementation of the Publish-Subscribe server. The server manages a number of different topics to which the clients can subscribe, unsubscribe and publish messages. To that end, clients send commands, which are handled by the server in a concurrent fashion.

Consider the model in Figure 5. The solid connectors between ports denote synchronizations, i.e., the execution of the corresponding transitions must be synchronized. In all synchronizations, data are exchanged between components. The dotted arrows from transitions to ports represent asynchronous communication realized by generating events corresponding to the spontaneous transitions of the receiving components.

The server consists of components of the six types shown in Figure 5. For each client, there is a dedicated TCPReader, responsible for receiving commands. Additionally, for each client there is a dedicated ClientProxy, responsible for receiving 1) acknowledgments that the client has been added or removed from a topic and 2) messages published from other clients registered in same topics. Thus each client is modeled by two dedicated components (a TCPReader and a ClientProxy), each modeling a distinct functional aspect of the client.

Upon reception by a TCPReader, each command is forwarded to the unique CommandBuffer component through the synchronization of the give and put enforceable transitions. The guard commandExists of the TCPReader is used to check whether it has received a new command and the guard notFull of the CommandBuffer is used to check whether the buffer is not full before receiving a new command (Figure 6: lines 29–30). If both guards evaluate to *true*, the command is transferred as data to the CommandBuffer (Figure 6: line 25).

The CommandBuffer is a passive component: the responsibility for retrieving commands from the CommandBuffer belongs to CommandHandlers. This happens through the synchronization of the handle and get enforceable transitions, when the notEmpty guard evaluates to *true* (Figure 6: lines 21–22). There can be arbitrarily many CommandHandlers that are concurrently handling commands. The CommandHandlers asynchronously forward commands to the TopicManager, by generating the event associated to the execute spontaneous transition of the TopicManager (Figure 7: lines 2 & 13). Notice that the @Data annotation is used to define input data necessary for the processing of spontaneous events (Figure 7: line 14). This mechanism allows CommandHandlers to send commands in the form of data to the TopicManager, in a manner very similar to asynchronous message passing.

```

1 @Ports({

@Port(name="put", type=PortType.enforceable),

@Port(name="get", type=PortType.enforceable)

3

4 })

5

6 @ComponentType(initial="0", name="CommandBuffer")

7 public class CommandBuffer {

private LinkedList<Command> commandList;

9

private int bufferSize;

10

11

public CommandBuffer(int bufferSize) {

12

this.bufferSize = bufferSize;

13

this.commandList = new LinkedList<Command>();

14

15

16

@Transition(name="get", source="0", target="0", guard="notEmpty")

17

public void get() {

18

commandList.remove();

19

20

@Guard(name="notEmpty")

21

22

public boolean notEmpty() { return !commandList.isEmpty(); }

23

2.4

@Transition(name="put", source="0", target="0", guard="notFull")

25

public void put(@Data(name="input") Command cmd) {

26

commandList.add(cmd);

27

28

29

@Guard(name="notFull")

30

public boolean notFull() { return commandList.size() < bufferSize; }</pre>

31

32

@Data(name="command")

33

public Command getNextCommand() { return commandList.get(0); }

34 }

```

Figure 6. Annotations for the CommandBuffer component type.

Depending on the type of the command (Figure 7: lines 16, 20, 24), the TopicManager asynchronously triggers one of the add, remove or publish transitions of the corresponding Topic (Figure 7: lines 18, 22, 26). The Topic executes the commands and triggers the corresponding transitions of a ClientProxy to either send an acknowledgment to the client in the case of the subscribe/unsubscribe commands or to distribute the message to all the subscribed clients of the topic in the case of a publish command. All transitions of TopicManager, Topic and ClientProxy components are spontaneous, i.e., they are executed asynchronously upon reception of the corresponding events.

An example of the above execution is the following: A TCPReader forwards the command subscribe epfl via data transfer through the synchronization of the give transition of the TCPReader with the put transition of the CommandBuffer. A CommandHandler receives the command from the CommandBuffer through the synchronization of the get and handle transitions. Then, the CommandHandler forwards the command to the TopicManager. This triggers the execute spontaneous transition during which the client reference is retrieved from the command and transferred to the epfl topic. This results in the asynchronous execution of the add transition of the epfl topic. During the execution of add the client reference, which was received though the data transfer, is stored and the name of the topic (epfl) is forwarded to the dedicated ClientProxy asynchronously via the data transfer. The ClientProxy stores the topic name and writes an acknowledgment in the socket, while executing the add spontaneous transition asynchronously.

Softw. Pract. Exper. (2016)

```

1 @Ports({

2

@Port (name="execute", type=PortType.spontaneous)

3 })

5 @ComponentType(initial="0", name="TopicManager")

public class TopicManager {

private HashMap<String, BIPActor> topics;

8

9

public TopicManager(HashMap<String, BIPActor> topics) {

10

this.topics = topics;

11

12

@Transition(name="execute", source="0", target="0")

13

public void execute(@Data(name="value") Command c) {

14

15

switch (c.getId()) {

16

case SUBSCRIBE:

17

Topic topic = topics.get(c.getTopic());

18

19

break;

20

case UNSUBSCRIBE:

21

Topic topic = topics.get(c.getTopic());

topic.remove(c.getClient()); // Generate a "remove" event in the topic

22

23

case PUBLISH:

2.4

25

Topic topic = topics.get(c.getTopic());

26

topic.publish(c.getClient(), c.getMessage());

27

// Generate a "publish" event in the topic

28

default:

2.9

break;

30

31

32 }

```

Figure 7. Annotations for the TopicManager component type.

## 3.3. Trackers and Peers example

The following example was initially presented in [11]. Although it is inspired by a wireless audio protocol for peer-to-peer communication, it should be noted that this example does not implement any kind of message passing (see also the discussion in Remark 4.2). Here, we provide it purely as an example of BIP model that will be used in Section 6.3 to stress-test the JavaBIP engine. Additionally, this example illustrates the use of n-ary connectors (here n=3) and of trigger ports.

There are two component types: Tracker and Peer. The protocol allows an arbitrary number of peers to communicate along an arbitrary number of wireless communication channels. Each channel is managed by a unique tracker.

The model for two peers and one tracker is shown in Figure 8. Peers are allowed to use at most one channel at a time. Access to channels is subject to the following registration mechanism. Every peer selects the channel it wants to use and registers through the register transition that is synchronized with the log transition of the tracker. During this synchronization, components are exchanging data. In particular, the tracker sends its identity to the peer and the peer stores it. Once registered, peers can either speak to the channel or listen to other registered peers in the channel. To ensure atomicity of each communication, every tracker enforces that 1) at most one registered component is speaking and 2) all other registered components are listening.

In the connectors enforcing the above constraints, the broadcast port of a tracker is a *trigger* (Section 4.1.2). This allows the broadcast transition to happen on its own, without requiring synchronization with transitions of other components. However, broadcast accepts synchronization with the speak and listen transitions. The listen and speak ports are *synchrons*, i.e., their corresponding transitions require synchronization with broadcast.

Figure 8. JavaBIP models of one tracker and two peers.

Peers can register (resp. unregister) through the register-log (resp. unregister-log) synchronization.

Notice that the interaction structure of the example is exponentially complex. In particular, the number of all possible interactions is  $(2^T - 1) \cdot (2^P + P \cdot 2^{P-1} + 2 \cdot P)$ , where P is the total number of peers and T is the total number of trackers.

To allow all peers to communicate with all trackers, all corresponding connectors must be present in the system. Data transfer (Section 4.2) is used to ensure that peers can interact only with the tracker they had previously been registered with: for each interaction, trackers propose their identity as data and peers use the idok guard to decide with which trackers they can synchronize. Thus, all transitions of the system are enforceable and in all possible interactions (except when a tracker is broadcasting without any registered peers) data are exchanged between components.

# 4. THEORETICAL FOUNDATIONS

In this section, we provide the formal component and coordination model underlying the JavaBIP framework. This model extends that of BIP [4, 8] by considering three types of transitions:

- enforceable transitions represent the controllable behavior of the component;

- *spontaneous* transitions represent changes in the environment that affect the component behavior, but cannot be controlled;

- internal transitions represent computations independent of the component environment.

We consider a system of components, each represented by a Finite State Machine (FSM) extended with ports and data. An FSM is specified by its states and the guarded transitions between them. Each transition has a function and a port associated to it. In general, one port can be associated to several transitions. However, the FSM is deterministic in the following sense: there cannot be two simultaneously enabled transitions leaving the same state that are both internal or both labeled by the same port.

For the sake of clarity, we will first present the model without data, then extend it by introducing data variables and data wires used for the transfer of values among the components.

## 4.1. Component model without data

4.1.1. Components and glue A component is a Finite State Machine (FSM) given by a quadruple  $C = (Q, P^e, P^s, \rightarrow)$ , where:

Softw. Pract. Exper. (2016)

- Q is a finite set of states,

- $P^e$  and  $P^s$  are disjoint finite sets of, respectively, enforceable and spontaneous ports,

•  $\rightarrow \subseteq Q \times P \times Q$ , with  $P = P^e \cup P^s \cup \{\tau\}$  and  $\tau \notin P^e \cup P^s$ , is a transition relation, where the special symbol  $\tau$  is used to label internal transitions.

Below, we will use the common notation, writing  $q \xrightarrow{p} q'$  as a shorthand for  $(q, p, q') \in \to$ . We say that a port  $p \in P$  is *enabled* in the state  $q \in Q$  iff there exists  $q' \in Q$ , such that  $q \xrightarrow{p} q'$ .

**Remark 4.1.** Notice that the above definition allows non-determinism in the component behavior. For the practical implementation, we require that all components be deterministic, i.e. such that, for any  $q \in Q$  and any  $p \in P$ , there is at most one outgoing transition from q labeled by p or, formally,  $|\{q' \in Q \mid (q, p, q') \in \to\}| \le 1$ . While this additional assumption does not have any impact on the theoretical foundations of the JavaBIP framework, as presented in this section, it noticeably simplifies the implementation.

Let  $C_i = (Q_i, P_i^e, P_i^s, \rightarrow)$ , for  $i \in [1, n]$ , be a set of components with pairwise disjoint sets  $P_i = P_i^e \cup P_i^s$ , i.e.,  $P_i \cap P_j = \emptyset$ , for all  $i \neq j$ . We denote  $P^e = \bigcup_{i=1}^n P_i^e$  and  $P^s = \bigcup_{i=1}^n P_i^s$ , respectively, the sets of all enforceable and spontaneous ports in the system.

Since our goal is to model interaction through synchronization among the actions performed by components, we introduce the notion of *interaction* as a non-empty set of enforceable ports  $a \subseteq P^e$ , such that  $|a \cap P_i^e| \le 1$ , for all  $i \in [1, n]$ , labeling the transitions to be synchronized. Indeed, we require that any interaction contain at most one port from any given component, reflecting the fact that a component can only execute one transition at a time.

The *glue* used to compose the components is the set of interactions that are allowed in the system. Let  $\gamma \subseteq 2^{P^e} \setminus \{\emptyset\}$  be such a set of interactions. The composition of components  $C_1, \ldots, C_n$  with the glue  $\gamma$  is the component  $\gamma(C_1, \ldots, C_n) = (Q, \gamma, P^s, \to)$ , where  $Q = \prod_{i=1}^n Q_i$  is the Cartesian product of the sets of states of the individual components and  $\to$  is the set of transitions defined as follows:

• for any  $i \in [1, n]$  and any spontaneous port  $p \in P_i^s$ ,

$$(q_1, \ldots, q_i, \ldots, q_n) \xrightarrow{p} (q_1, \ldots, q'_i, \ldots, q_n) \iff q_i \xrightarrow{p} q'_i,$$

• similarly for internal transitions, for any  $i \in [1, n]$ ,

$$(q_1, \ldots, q_i, \ldots, q_n) \xrightarrow{\tau} (q_1, \ldots, q_i', \ldots, q_n) \iff q_i \xrightarrow{\tau} q_i',$$

• for any interaction  $a \in \gamma$ ,

$$(q_1, \dots, q_n) \xrightarrow{a} (q'_1, \dots, q'_n) \iff \begin{cases} q_i \xrightarrow{p_i} q'_i, & \text{if } a \cap P_i^e = \{p_i\}, \\ q_i = q'_i, & \text{if } a \cap P_i^e = \emptyset. \end{cases}$$

Thus, the notion of enabledness is extended from ports to interactions: an interaction  $a \in \gamma$  is enabled in  $\gamma(B_1,\ldots,B_n)$ , only if, for each component  $C_i$  participating in a—that is, such that  $a \cap P_i^e = \{p_i\}$ , for some  $p_i \in P_i^e$ —the port  $p_i$  is enabled in  $C_i$ . Notice that the states of components that do not participate in the interaction remain unchanged. Observe also that  $\gamma$  defines the set of *allowed* interactions: it is possible that an interaction  $a \in \gamma$  is never actually enabled in  $\gamma(C_1,\ldots,C_n)$ .

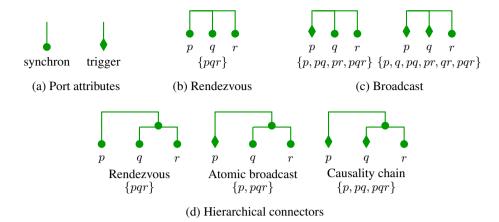

4.1.2. Connectors Interactions among the enforceable ports of the system components are specified by connectors [8]. A connector defines a set of interactions based on the synchronization attributes of the connected ports, which may be either synchron or trigger (Figure 9a):

• if all connected ports are synchrons, then synchronization is by *rendezvous*, i.e., the connector defines exactly one interaction, which comprises all its ports (Figure 9b);

<sup>§</sup>Here and below, we omit the index on transition relations →, since it is always clear from the context.

Figure 9. BIP connectors: below each connector, we show the set of interactions it defines

• if the connector has at least one trigger, the synchronization is by *broadcast*, i.e., the connector defines the set of interactions comprised by all non-empty subsets of the connected ports containing at least one of the trigger ports (Figure 9c).

**Remark 4.2.** Notice that our use of the terms "broadcast" and "atomic broadcast" is very different from the meaning commonly used in distributed computing, where messages are broadcast to a number of recipients through a network. In this paper, we use the terms "rendezvous", "broadcast" and "atomic broadcast" for the sake of homogeneity with previous work on BIP (e.g. [8]), to denote different kinds of connectors as described above. The use of the term "broadcast" in [8] was inspired by previous work on Statecharts [16].

The same principle is recursively extended to hierarchical connectors, where one interaction from each subconnector is used to form an allowed interaction according to the synchron/trigger labeling of the connector nodes. For instance the causal chain connector in Figure 9d has the port p labeled as a trigger, whereas the binary broadcast subconnector q-r is labeled as a synchron. Thus the causal chain connector allows the singleton interaction p and any interaction that combines p with some interaction of the subconnector. Since the latter allows interactions q and qr, this results in three interactions allowed by the hierarchical connector: p, pq and pqr.

When, as in the examples of Section 3, there are several connectors in a system, the allowed interactions are precisely those that are defined by at least one connector.

Among the connectors in the examples of Section 3, Camel Routes and Publish Subscribe Server rely on strong binary rendezvous. The Trackers and Peers example uses weak (broadcast) synchronization defined by ternary connectors with triggers.

4.1.3. Boolean encoding of the connectors and macro notation Connectors are very convenient for graphical design and representation of interaction sets. However, their use requires the knowledge of all components (hence also all ports) in the system. In JavaBIP, we have opted for a macro notation similar to that introduced in [11]. This notation imposes synchronization constraints based on the component types, rather than on the component instances, allowing for a better separation between component and glue specification. It is based on the Boolean characterization of connectors [17], which we succinctly present below, before introducing the macro notation.

Consider a set of interactions  $\gamma \subset 2^{P^e}$ , where  $P^e$  is the set of all enforceable ports in the system. This set can be characterised by a Boolean predicate  $\phi_{\gamma} \in \mathbb{B}[P^e]$  on the set of enforceable ports: an interaction  $a \subseteq P^e$  belongs to  $\gamma$  if and only if the valuation, which assigns to each port  $p \in P^e$  the value true if  $p \in a$  and false otherwise, satisfies  $\phi_{\gamma}$ . The predicate  $\phi_{\gamma}$  is called the *characteristic predicate* of  $\gamma$  and is defined by putting

$$\phi_{\gamma} = \bigvee_{a \in \gamma} \left( \bigwedge_{p \in a} p \wedge \bigwedge_{p \in P^e \setminus a} \overline{p} \right).$$

Copyright © 2016 John Wiley & Sons, Ltd. Prepared using speauth.cls

Table I. Boolean encoding of connectors in Figure 9 (we omit the common conjunct  $(a \lor b \lor c)$ )

| Name             | Set of allowed interactions | Boolean encoding                                                       |

|------------------|-----------------------------|------------------------------------------------------------------------|

| Rendezvous       | $\{pqr\}$                   | $(p \Rightarrow qr) \land (q \Rightarrow pr) \land (r \Rightarrow pq)$ |

| Broadcast 1      | $\{p, pq, pr, pqr\}$        | $(q \Rightarrow p) \land (r \Rightarrow p)$                            |

| Broadcast 2      | $\{p,q,pq,pr,qr,pqr\}$      | $(r \Rightarrow p \lor q)$                                             |

| Atomic broadcast | $  \{p, pqr\}$              | $(q \Rightarrow pr) \land (r \Rightarrow pq)$                          |

| Causality chain  | $\{p,pq,pqr\}$              | $(q \Rightarrow p) \land (r \Rightarrow q)$                            |

Notice, however, that, for a given  $\gamma$ , this predicate can be equivalently written in a different form. For example, consider the left-hand side connector in Figure 9c with  $P^e = \{p, q, r\}$  and  $\gamma_{bdc} = \{p, pq, pr, pqr\}$ . Omitting, for clarity, the conjunction operator, we then have

$$\phi_{\gamma_{bdc}} = p\,\overline{q}\,\overline{r} \ \lor \ p\,q\,\overline{r} \ \lor \ p\,\overline{q}\,r \ \lor \ p\,q\,r \equiv p\,,$$

which corresponds, indeed, to the meaning defined above: this connector allows any interaction among the ports p, q and r that contains p. Similarly, for the causality chain in Figure 9d, we have  $\gamma_{cc} = \{p, pq, pqr\}$ , characterised by

$$\phi_{\gamma_{cc}} = p \, \overline{q} \, \overline{r} \, \vee \, p \, q \, \overline{r} \, \vee \, p \, q \, r \equiv p \wedge (r \Rightarrow q) \, .$$

Here, the meaning of the implication  $r \Rightarrow q$  is that the participation of the port r in any interaction requires that of the port q. Finally, observe that  $\phi_{\gamma_{cc}}$  can also be equivalently rewritten as

$$\phi_{\gamma_{cc}} \equiv (p \lor q \lor r) \land (q \Rightarrow p) \land (r \Rightarrow q), \tag{1}$$

which makes all such requirements explicit. Indeed the second and third conjuncts in (1) explicitate the causal dependencies visible in the connector structure, whereas the first conjunct simply states that at least one port must participate in any interaction. In [17], we have shown that the set of interactions defined by any connector can be characterised by a Boolean formula similar to (1), where the implications in each conjunct take the form

$$p \Rightarrow a_1 \vee \cdots \vee a_n$$

, (2)

Softw. Pract. Exper. (2016)

DOI: 10.1002/spe

with p being a port and each  $a_i$  being a conjunction of several ports. In the implication (2), we call p the *effect*, whereof  $a_1, \ldots, a_n$  are the *causes*. Indeed, for p to participate in an interaction, all the ports belonging to at least one of  $a_1, \ldots, a_n$  must participate. Thus, we can say that the participation of  $a_i$ , for some  $i \in [1, n]$ , in an interaction *is the reason why p can participate*. Table I provides the encodings of all the connectors shown in Figure 9.

Similarly to [11], we use the macro

$$p$$

Require  $a_1; \ldots; a_n$

to specify the constraint (2). For example the encodings of Broadcast 2 and Atomic broadcast (Table I) are, respectively,

$$r$$

Require  $p;q$  and

$$\begin{cases} q$$

Require  $pr \\ r$  Require  $pq$ .

Notice the semicolon in the left-hand side macro.

In the commonly encountered systems, such as the examples in Section 3, most of the ports participate in very few connectors. In the constraints (1), this translates by conjuncts of the form

The notation used in [11] differs from JavaBIP in that it uses the additional Unique macro to specify cardinality exactly one, which in JavaBIP is expressed directly in the Require macro. Additionally, in [11] it is not possible to express exact cardinalities larger than one.

$p \Rightarrow false$ , meaning that the port p cannot participate in any interaction allowed by the connector. However, adding such conjuncts explicitly for all ports that do not participate in a connector is rather tedious. Furthermore, it is often convenient to define the constraints for a subsystem, independently of the way it will be used. In such case, some ports of the system, which will not participate in the defined interactions, are not yet known. Hence, one needs a notation to specify that only a certain set of ports can participate in an interaction that contains p, other ports being implicitly excluded. This is achieved by the macro

$$p \ \ \mathbf{Accept} \ \ a\,, \qquad \text{ which formally means } \qquad p \Rightarrow \bigwedge_{\substack{q \in P^e \backslash a \\ q \neq p}} \ \overline{q}\,.$$

The macro Accept is defined for a single port, therefore for a port r to participate in the interaction that contains p, it must be accepted by every other port participating in the interaction.

4.1.4. Macro notation based on component types In the previous subsection, we have introduced the Require-Accept macro notation for the definition of glue for a system consisting of a given set of components. Similarly to [11], JavaBIP relies on component types, rather than on component instances for the definition of glue. Although this approach is less expressive—it only allows the definition of regular glue, which imposes the same synchronization constraints on all instances of a given component type—, it provides better separation between glue and component specification. It is sufficient for practical purposes: firstly, finer specification can be obtained by considering component subtypes and, secondly, data variables and transfer (see Section 4.2) can be used by a component to remember the identities of other components it interacted with and use them to restrict subsequent interactions (e.g., continue interacting with the same component as in the previous cycle).\*\*

Let  $\mathcal{T}$  be a set of component types. Each *component type* represents a set of component instances with identical interfaces and behavior. For a component type  $T \in \mathcal{T}$ , we will write C:T to denote a component C of type T; we denote T.p the *port type* p, i.e., a port belonging to the interface of the type T, and C.p, for a component C:T, the *port instance* of the type T.p; finally, we denote  $C.P^e$  the set of all enforceable ports of the component C.

We are now in position to extend the Require-Accept macro notation to component types. Let  $T^1, T^2 \in \mathcal{T}$  be component types and let  $C_i^1: T^1$  and  $C_j^2: T^2$  (with  $i \in [1, n], j \in [1, m]$ ) be the corresponding component instances. We define

$$T^1.p \ \ \mathbf{Require} \ \ T^2.q \qquad \equiv \qquad \bigwedge_{i=1}^n \left( C_i^1.p \ \Rightarrow \ \bigvee_{j=1}^m \left( C_j^2.q \land \bigwedge_{k\neq j} \overline{C_k^2.q} \right) \right) \, ,$$

which means that, to participate in an interaction, each of the ports  $C_i^1 cdot p$  (with  $i \in [1, n]$ ) requires the participation of *precisely one* of the ports  $C_j^2 cdot q$  (with  $j \in [1, m]$ ). This is in contrast with the meaning used in [11], where a separate macro is used to enforce uniqueness of the cause port. Thus, we have opted for a macro notation where the cardinality of the causes is explicit: should two instances of the same port type be required, this is specified by explicitly putting the cause port type twice:

$$T^1.p \ \ \mathbf{Require} \ \ T^2.q \ T^2.q \qquad \equiv \qquad \bigwedge_{i=1}^n \left( C_i^1.p \ \Rightarrow \ \bigvee_{j=1}^m \bigvee_{k\neq j} \left( C_j^2.q \ C_k^2.q \wedge \bigwedge_{l\neq j,k} \overline{C_l^2.q} \right) \right)$$

and so on for higher cardinalities. This choice of notation is motivated by our observation that cardinalities higher than one are very rare in practical examples.

Softw. Pract. Exper. (2016)

This is equivalent to (2) with the empty list of causes.

<sup>\*\*</sup>This is similar to the use of history variables in [11].

Similarly, we define the notation for the Accept macro for component types:

$$\begin{array}{lll} T^1.p \ \ \mathbf{Accept} \ \ T^2.q & \equiv & \bigwedge_{i=1}^n \left( C_i^1.p \ \Rightarrow & \bigwedge_{r \in P^e \backslash \{C_j^2.q \ | \ j \in [1,m]\}} \ \overline{r} \right) \\ \\ \text{where} & P^e & = & \bigcup_{T \in \mathcal{T}} \bigcup_{C:T} C.P^e \, . \end{array}$$

The generalization of the above definitions to more complex macros is straightforward, but cumbersome. Therefore we omit it here.

**Example 4.3.** To illustrate the use of the above macro notation, let us consider the Camel routes example (Section 3.1). The glue constraints imposed by the connectors in Figure 2 are specified by the following combination of macros:

Monitor.add Require Route.on

Monitor.rm Require Route.finished

Route.on Require Monitor.add

Route.finished Require Monitor.rm

Route.off Require

Monitor.add Accept Route.on

Monitor.rm Accept Route.finished

Route.on Accept Monitor.add

Route.finished Accept Monitor.rm

Route.off Accept -

where the dashes '-' in the last line indicate that the port Route.off neither requires, nor accepts synchronization with any other port. Recall that the port Route.end is spontaneous. Hence, it does not have any associated glue constraints. Finally, notice that this set of macros is independent from the number of Camel routes in the system.

**Example 4.4.** Now, let us consider an alteration of the previous example, where we require that the Monitor component removes two routes simultaneously at the execution of the port rm. Thus, in the require macro for the rm port type, the cardinality of the causes must be equal to two. This is specified by putting the cause port type finished twice as shown below:

Monitor.add Require Route.on

Monitor.rm Require Route.finished

Route.finished

Route.on Require Monitor.add

Route.finished Route.finished

Route.finished Route.finished Route.finished

Route.finished Require Monitor.rm

Route.finished Route.off Require

Route.off Accept Monitor.rm

Route.finished

Route.off Accept -

Notice that the accept macro for the finished port type has also changed, by *accepting* not only rm but also finished.

Softw. Pract. Exper. (2016)

```

A.a Require B.b B.b

B.b Require A.a C.c; C.c C.c

B.b Accept A.a B.b C.c

C.c Require —

C.c Accept A.a B.b C.c

```

Notice that by the combination of the first two require macros, a synchronization involving exactly an instance of A. a and two instances of B. b is not allowed, since B. b requires at least one instance of C. c to also participate in the synchronization.

**Example 4.6.** The set of interactions allowed by the connectors in the Trackers and Peers example (Section 3.3) can be specified as follows (notice the semicolon in the require constraint for Tracker.log):

```

Peer.speak

Require

Tracker.broadcast

Peer.speak

Accept

Tracker.broadcast Peer.listen

Peer.listen

Require

Tracker.broadcast

Peer.listen

Accept

Tracker.broadcast Peer.speak

Peer.listen

Peer.register

Require

Tracker.log

Peer.register

Accept

Tracker.log

Peer.unregister

Require

Tracker.log

Peer.unregister

Accept

Tracker.log

Tracker.broadcast

Require

Tracker.broadcast

Accept

Peer.speak

Peer.listen

Tracker.log

Require

Peer.register;

Peer.unregister

Tracker.log

Accept

Peer.register

Peer.unregister

```

## 4.2. Extension of the model with data

4.2.1. Components with data Data transfer is essential to allow information flow between components. For each component we consider two types of data:

- input data that the component receives from its environment (including other components);

- output data that the component provides to other components.

To each type of data we associate the corresponding set of variables. For simplicity, we assume in this section that all variables have the same domain  $\mathcal{D}$ . In our implementation, variables can have any type that can be defined in a Java program.

In the presence of data, the state of a component is defined by the combination of the control location and the valuation of its output variables. Since the input data are provided by the environment, they do not contribute to the state of the component. This is analogous to the combination of the program counter and the valuation of variables in the semantics of programming languages. In the absence of data (Section 4.1), the state and the control location coincide. Therefore, for the sake of presentation uniformity, we will continue referring as "state" to the control location of the FSM underlying the component; we will refer as "complete state" to the combination of the control location and the valuation of output variables.

Let us first introduce some additional notation. Assume that  $X^{in}$  and  $X^{out}$  are two given sets of, respectively, input and output variables of a component. We denote

```

\mathbb{B}[X^{in},X^{out}]\,,\qquad \text{the set of Boolean predicates on input and output variables,}\\ \mathbb{E}[X^{in},X^{out}]\,,\qquad \text{the set of assignment expressions of the form }Y:=e(X), \text{ with }\\ X\subset X^{in}\cup X^{out} \text{ and }Y\subset X^{out}.

```

For a guard  $g \in \mathbb{B}[X^{in}, X^{out}]$  or an expression  $f \in \mathbb{E}[X^{in}, X^{out}]$ , we denote  $in(g), in(f) \subseteq X^{in}$  and  $out(g), out(f) \subseteq X^{out}$  the corresponding sets of input and output variables used in g and f. A component with data is a tuple  $C = (Q, P^e, P^s, X^{in}, X^{out}, d, \rightarrow)$ , where:

Softw. Pract. Exper. (2016)

Figure 10. Example of a non-deterministic component with data

- Q is a finite set of states,

- $P^e$  and  $P^s$  are disjoint finite sets of, respectively, enforceable and spontaneous ports,

- $X^{in}$  and  $X^{out}$  are disjoint finite sets of, respectively, input and output variables,

- $d: P^e \to 2^{X^{out}}$  is a *data access mapping*, associating to each enforceable port  $p \in P^e$  the set of output variables that are accessible through p;

- $\rightarrow \subseteq Q \times P \times \mathcal{G} \times \mathcal{F} \times Q$  is a transition relation (as above, we write  $q \xrightarrow{p,g,f} q'$  as a shorthand for  $(q,p,g,f,q') \in \rightarrow$ ), where

- $\mathcal{G} = \mathbb{B}[X^{in}, X^{out}]$  is a set of *guards*,

- $\mathcal{F} = \mathbb{E}[X^{in}, X^{out}]$  is a set of update expressions,

- $P = P^e \cup P^s \cup \{\tau\}$  with  $\tau \notin P^e \cup P^s$ ,

such that  $in(f) = in(g) = \emptyset$ , for any internal transition  $q \xrightarrow{\tau,g,f} q'$ .

**Example 4.7.** This definition of components with data can be illustrated by the listings in Figure 3 and 4. In Figure 3, there is only one @Data annotation (lines 44–45) associated to a method. It defines the output variable deltaMemoryOnTransition (see Section 5.1 for the detailed presentation of the @Data annotation). Thus, we have  $X^{in} = \emptyset$  and  $X^{out} = \{\text{deltaMemoryOnTransition}\}$ . Furthermore, the fields accessTypePort and ports indicate that this output variable can be accessed through ports on and finished. Thus the data access mapping is given by:

$$d = \left\{ egin{array}{ll} ext{on} \mapsto \left\{ ext{deltaMemoryOnTransition}

ight\}, \ ext{off} \mapsto \emptyset\,, \ ext{finished} \mapsto \left\{ ext{deltaMemoryOnTransition}

ight\} \end{array}

ight\}.$$

The @Data annotations in the listing in Figure 4 (lines 18, 23 and 28) are associated to method parameters. They define three utilisations of the same input variable memoryUsage. Thus, we have  $X^{in} = \{\text{memoryUsage}\}, X^{out} = \emptyset$  and, since there are no output variables, the data access mapping is constant:  $d(p) = \emptyset$ , for all ports  $p \in P^e$ .

**Remark 4.8.** Similarly to Remark 4.1, the above definition of components with data allows non-deterministic behavior. In the practical implementation, we require that all components be deterministic, i.e. we require that for any port  $p \in P$  and any complete state (q, v), with state  $q \in Q$  and valuation of variables  $v: X^{in} \cup X^{out} \to \mathcal{D}$ , we have  $|\{(g, f, q') \in \mathcal{G} \times \mathcal{F} \times Q \mid q \xrightarrow{p,g,f} q', g(v) = true\}| \leq 1$ .

Notice that, as opposed to Section 4.1.1, in a component with data, there can be several outgoing transitions in the same state, labeled with the same port. However, we require that at most one of

them be enabled—meaning that its guard evaluates to true—with any valuation of the component variables. For example, consider the component shown in Figure 10. Although there are three outgoing transitions in state value labelled with the same port test, this component is, indeed, deterministic, since only one of these transitions can be enabled, for any value of x.

The input variables do not have persistent values—they represent the arguments of transition guards and update expressions, and have to be assigned a value provided by the environment every time, when the corresponding guard or update expression must be evaluated. Hence, indeed, the sets  $X^{in}$  and  $X^{out}$  are disjoint.

As mentioned above, at any given execution cycle, the complete state of the component is formed by the combination of its current control location and the valuation of its output variables. The component can change its complete state by executing a transition only if its environment provides all the necessary inputs—i.e., the input data required by the guard and the update expression of the transition—and the guard is satisfied. Upon executing the transition the values of the output variables are modified using the update expression. Notice that the values of the output variables that a component provides are those before the execution of the transition. Furthermore, these need not be the same as the output variables updated by the transition. In other words, for a transition  $q \xrightarrow{p,g,f} q'$ , with  $p \in P^e$ , there is no a priori relation between d(p) and out(f).

We denote  $\widetilde{C} = (Q, P^e, P^s, \rightarrow_{da})$ , with  $q \xrightarrow{p}_{da} q'$  iff  $q \xrightarrow{p,g,f} q'$ , for some  $g \in \mathcal{G}$  and  $f \in \mathcal{F}$ , the component obtained by abstracting the data from the component with data  $C = (Q, P^e, P^s, X^{in}, X^{out}, d, \rightarrow)$ .

4.2.2. Composition Let  $C_i = (Q_i, P_i^e, P_i^s, X_i^{in}, x_i^{out}, d_i \rightarrow)$ , for  $i \in [1, n]$ , be a set of components with data with pairwise disjoint sets of ports  $P_i = P_i^e \cup P_i^s$  and variables  $X_i = X_i^{in} \cup X_i^{out}$ , i.e.,  $P_i \cap P_j = X_i \cap X_j = \emptyset$ , for all  $i \neq j$ . We denote  $P^e = \bigcup_{i=1}^n P_i^e$  and  $P^s = \bigcup_{i=1}^n P_i^s$ , respectively, the sets of all enforceable and spontaneous ports in the system;  $X^{in} = \bigcup_{i=1}^n X_i^{in}$  and  $X^{out} = \bigcup_{i=1}^n X_i^{out}$ , respectively, the sets of all input and output variables.

The glue defining the composition of components with data comprises, in addition to a set of interactions  $\gamma \subseteq 2^{P^e}$ , the *data wire* relation  $\delta \subseteq X^{in} \times X^{out}$ , associating input and output variables in the system.

We say that the system is *closed* if, for each interaction allowed by  $\gamma$ , all input variables have corresponding output variables. Denoting, for an interaction  $a=\{p_i\,|\,i\in I\}\in\gamma$ ,  $in(a)=\bigcup_{i\in I}\left(in(g_i)\cup in(f_i)\right)$  and  $out(a)=\bigcup_{i\in I}d(p_i)$ , this can be formally defined as follows: for any set of component transitions  $\{q_i\stackrel{p_i,g_i,f_i}{\longrightarrow}q_i'\,|\,i\in I\}$ , holds the property

$$\forall x \in in(a), (\exists x' \in out(a) : (x, x') \in \delta).$$

A given interaction is possible in the composed system  $\delta\gamma(C_1,\ldots,C_n)$  if and only if the same interaction would be possible in the data-abstract system  $\gamma(\widetilde{C}_1,\ldots,\widetilde{C}_n)$  and, for each of the involved components, all the necessary inputs—i.e., the input data required by the guard and the update expression of the corresponding transition—are available and the guard is satisfied.

Formally, the composition is defined as  $\delta\gamma(C_1,\ldots,C_n)=(Q,\gamma,P^s,X^{in},X^{out},d\to)$ , where  $Q=\prod_{i=1}^nQ_i$  is the Cartesian product of the sets of states of the individual components, the data access mapping is defined, for any interaction  $a=\{p_i\mid i\in I\}$ , by letting

$$d(a) = \bigcup_{i \in I} d_i(p_i),$$

and  $\rightarrow$  is the set of transitions defined as follows:

• for any  $i \in [1, n]$  and any spontaneous port  $p \in P_i^s$ ,

$$(q_1, \ldots, q_i, \ldots, q_n) \xrightarrow{p,g,f} (q_1, \ldots, q'_i, \ldots, q_n) \iff q_i \xrightarrow{p,g,f} q'_i,$$

• similarly for internal transitions, for any  $i \in [1, n]$ ,

$$(q_1, \ldots, q_i, \ldots, q_n) \xrightarrow{\tau, g, f} (q_1, \ldots, q'_i, \ldots, q_n) \iff q_i \xrightarrow{\tau, g, f} q'_i,$$

• for any interaction  $a = \{p_i \mid i \in I\} \in \gamma$  and any mapping  $\delta' : in(a) \to out(a)$ , such that  $(x, \delta'(x)) \in \delta$ , for any  $x \in in(a)$ ,

$$(q_1, \dots, q_n) \xrightarrow{a,g,f} (q'_1, \dots, q'_n) \iff \begin{cases} q_i \xrightarrow{p_i, g_i, f_i} q'_i, & \text{if } i \in I, \\ q_i = q'_i, & \text{if } i \notin I, \\ g = \bigwedge_{i \in I} \widetilde{g}_i, \\ f = (\widetilde{f}_i)_{i \in I}, \end{cases}$$

where  $\widetilde{g}_i$  and  $\widetilde{f}_i$  denote the expressions obtained, respectively, from  $g_i$  and  $f_i$ , by substituting each input variable x by the corresponding output variable  $\delta'(x)$ ; and  $\left(\widetilde{f}_i\right)_{i\in I}$  denotes the combined execution of the update expressions  $\widetilde{f}_i$ .

Notice that, in the definition of f, all the assignments are executed in parallel using the previous values provided as inputs to the component update expressions. Hence, the order of updates is irrelevant.

The presentation in this section has provided the theoretical foundations for the implementation of the JavaBIP Executor class and Engine, on one hand, and the component and glue specifications, on the other hand. Indeed, the Executor and the Engine (Section 6) implement, respectively, the semantics of components (Section 4.2.1) and glue (Section 4.2.2). In Section 5, we present the various syntactic constructs used to define JavaBIP systems. Java annotations used for the definition of BIP Specifications (Section 5.1) are based on the component model defined in Sections 4.1.1 and 4.2.1. The XML formats used for the definition of glue constraints (Section 5.2) and data wires (Section 5.3) directly mirror the corresponding formalizations in Sections 4.1.4 and 4.2.2. Short of a formal proof, this close link between the formal model and the implementation provides a high degree of confidence in the correctness of the framework. Furthermore, it enables the JavaBIP-to-BIP transformation, for the connection with the various analysis tools available in the BIP tool-set as discussed in Section 2.

# 5. SYSTEM SPECIFICATION

The following subsections present the constructs used to provide behavior, glue and data-wire specifications (Figure 1 step ①). We refer to the examples of Section 3 to illustrate these constructs.

# 5.1. Behavior specification

Developers must specify component behavior through FSMs extended with ports and data. An FSM has states and guarded transitions between them. Each transition has a method and a port associated with it. Although, in general, one port can be associated with several transitions, such transitions must have different origin state. In other words, FSMs are deterministic: there cannot be two transitions leaving the same state and labeled by the same port.

The Behavior specification can be provided via annotations associated with class, method and parameter declarations. To write a Behavior specification, developers must use the following annotations:

- @ComponentType: Annotates a Java class. Declares a component type by specifying its name and the initial state of the underlying FSM (Figure 7: line 5).

- @Port: Annotates a Java class. Declares a port by specifying its name and type—"spontaneous" or "enforceable" (Figure 7: line 2).

- @Ports: Annotates a Java class. Groups all @Port annotations associated to a given component type (Figure 7: line 1).

- @Guard: Annotates a method returning a Boolean value. Declares that the method can be used as part of a transition guard, by specifying the guard name (Figure 6: line 21).

- @Transition: Annotates a method returning void. Declares an FSM transition, by specifying the name of the corresponding port, the source and the target states, and the guard, which is a Boolean expression on the guard names declared with the @Guard annotation (Figure 6: line 16). Guard expressions can be defined using parenthesis and three logical operators: negation '!', conjunction '&' and disjunction '|'.

The type of the transition is defined by that of the port it is labeled with (Figure 6: lines 2–3 and Figure 7: line 2). Internal transitions are specified by leaving the transition name empty (Figure 3: line 32).

- @Data: Annotates a non-void method or a method parameter. Defines the data required (input) or provided (output) by the component:

- input datum, when associated with a parameter of a guard or transition method (Figure 7: line 14):

- output datum, when associated with a method returning a value (Figure 6: line 32).

@Data annotations always have the field name. Data names are used to establish connections (called *data wires*—see Section 5.3) between inputs and outputs provided by the application components. When the @Data annotation is used to define an output datum, it has two additional fields: accessTypePort (allowed, disallowed or any) and ports. The latter is a list of ports of the component in question, which is used to specify how this datum can be accessed, based on the value of the accessTypePort field:

- allowed means that the datum can be accessed only through the ports in ports;

- disallowed means that the datum can be accessed only through the ports not in ports;

- any means that the datum can be accessed at any execution point—the list of ports must be empty.

Notice that the output values are provided by the @Data-annotated methods. The methods associated to transitions do not return any value—they must be declared as public void.

The usage of data as parameters in guards allows components to disable interactions based on the data values proposed by other components. For example, in Figure 4, transition add (lines 16–20) depends on the guard hasCapacity, which requires the datum memoryUsage (lines 27–30). This datum is received from another component potentially participating in an interaction. If the proposed datum does not satisfy the guard, the interaction among these particular components is disabled.

# 5.2. Glue specification

To define the interaction model, a developer must specify the interaction constraints of the system; i.e., which ports of different components must synchronize. Interaction constraints need to be specified once for each *component type* of the system. For instance, in the Publish-Subscribe example of Figure 5, many instances of readers may exist in the system, however, the interaction model of the TCPReader component type needs to be specified only once.

Interaction constraints are specified using macro-notation:

• Causal constraints (Require) specify ports of other components, necessary for any interaction involving the port with which the constraint is associated.

```

1 <require>

<effect id="give" specType="TCPReader"/>

3

<causes>

4

<port id="put" specType="CommandBuffer"/>

5

</causes>

6 </require>

7 <accept>

8

<effect id="give" specType="TCPReader"/>

9

<causes>

<port id="put" specType="CommandBuffer"/>

1.0

11

</causes>

12 </accept>

```

Figure 11. Glue specification for the Publish-Subscribe example (cf. Section 3.2).

```

1 <require>

<effect id="broadcast" specType="Tracker"/>

3

<causes>

</causes>

4

5 </require>

6 <accept>

7

<effect id="broadcast" specType="Tracker"/>

8

<causes>

9